CADSTAR cho kỹ sư thiết kế điện tử

Sự sáng tạo

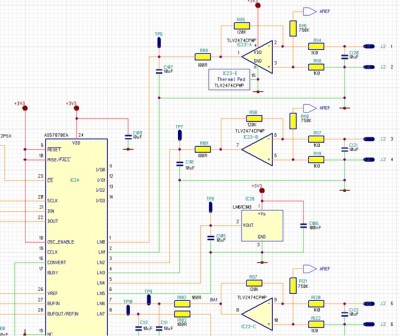

Những thách thức về thiết kế PCB của bạn đòi hỏi các giải pháp sáng tạo, do đó có thể nắm bắt ý tưởng của bạn một cách nhanh chóng, hiệu quả, không có lỗi là rất quan trọng. CADSTAR Schematic Capture cung cấp cho bạn một nền tảng thiết kế linh hoạt, nhưng mạnh mẽ, bao gồm:

- Lựa chọn phương pháp thiết kế cho phép bạn thiết kế ở cấp độ biểu tượng, một phần, khối hoặc trang tính với môi trường thiết kế phân cấp nhiều lớp hoặc nhiều trang.

- Một cơ sở dữ liệu thông minh, liên kết thu thập chính xác mục đích thiết kế và duy trì tính toàn vẹn thiết kế trong suốt luồng CADSTAR.

- Một môi trường thiết kế hoàn toàn có thể tùy chỉnh với cùng một giao diện đồ họa trong Sơ đồ mạch, Bố trí PCB, Thư viện và Môi trường định tuyến.

- Một loạt các công cụ hỗ trợ để giúp bạn xác định, mô phỏng và quản lý dữ liệu thiết kế của bạn

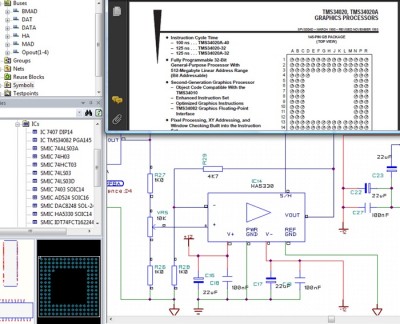

Quản lý thư viện

Thư viện là chìa khóa cho quá trình thiết kế, vì vậy Zuken giúp bạn vượt qua trò chơi bằng thư viện trực tuyến với hơn 250.000 phần từ các nhà cung cấp hàng đầu như Actel, Analog Devices, Intel, Texas và Zetex. Liên kết động có thể được thêm vào biểu dữ liệu hoặc trang web của nhà cung cấp để các kỹ sư có thông tin mới nhất.

Nếu bạn cần tích hợp dữ liệu CAD với cơ sở dữ liệu kỹ thuật của bạn, CADSTAR hỗ trợ truy cập vào bất kỳ nguồn dữ liệu tương thích ODBC nào, cho phép liên kết đến thông tin doanh nghiệp mới nhất cũng như khả năng chạy tìm kiếm tham số để xác định đúng phần bằng cách sử dụng một loạt thuộc tính.

Độ lặp lại

Bạn cần bao gồm các khối thiết kế ‘mạch vàng’ lặp lại hoặc được xác định trước? Tạo chúng dưới dạng các khối tái sử dụng và xây dựng thư viện của riêng bạn để chia sẻ với đồng nghiệp. Việc tái sử dụng khối trong sơ đồ có thể tự động liên kết với các khối chèn sẵn trong bố cục PCB, bao gồm vị trí, định tuyến, đồng và văn bản để giúp bạn tiết kiệm thời gian và nâng cao chất lượng trong khi bố cục và kiểm tra.

Tích hợp FPGA

Ngày càng nhiều mẫu thiết kế bao gồm các thiết bị có thể lập trình cho phép bạn mở rộng và tùy chỉnh chức năng của sản phẩm. Các thiết bị có dung lượng cao ngày nay có số lượng pin cao giúp định nghĩa biểu tượng và quản lý kết nối pin ngày càng phức tạp; không chỉ trong sơ đồ mà còn trong suốt quá trình thiết kế.

CADSTAR FPGA, được thành lập dựa trên công nghệ hàng đầu từ Aldec Inc cho phép phát triển, tổng hợp và xác minh FPGA bằng cách sử dụng phương pháp thiết kế trực quan độc lập với nhà cung cấp. Việc chuyển giao thông tin pin một lần nhấp đến và từ CADSTAR cho phép tạo nhanh các hiệu ứng khối chức năng và đồng bộ hóa các thay đổi về pin để tối ưu hóa khả năng định tuyến và hiệu suất của thiết kế.

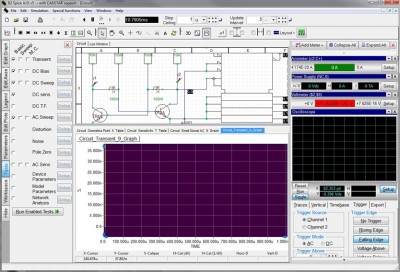

Mô phỏng

CADSTAR hỗ trợ các công cụ để mô phỏng chế độ tương tự, kỹ thuật số và chế độ hỗn hợp. Bạn có thể xuất một netlist Spice để mô phỏng.

Quản lý biến thể

Trình quản lý biến thể cho phép bạn xác định các sản phẩm theo thị trường cụ thể mở rộng phạm vi và sự hấp dẫn của phạm vi của bạn, cải thiện kiểm soát chi phí và tính đa dạng sản phẩm. CADSTAR cho phép bạn tạo, xem và liệt kê nhiều biến thể thiết kế bằng cách loại trừ các mục đã chọn hoặc chỉ định các phần thay thế.

Thiết kế theo hướng hạn chế

Ngay cả bộ xử lý và bộ nhớ hiện đại đơn giản nhất sử dụng giao diện DDR, do đó việc thêm các ràng buộc pin, net và thời gian quan trọng trực tiếp vào thiết kế mạch logic là rất hợp lý. Trình duyệt hạn chế CADSTAR là môi trường lý tưởng để nhập và quản lý ngay cả những quy tắc phức tạp nhất, sử dụng giao diện kiểu bảng tính quen thuộc giúp nắm bắt và ghi lại ý định thiết kế.

Lập kế hoạch vị trí

Đúng vị trí của các khối thiết kế hoặc thậm chí các thành phần riêng lẻ, ngày càng quan trọng vì biên độ nhiễu giảm và tốc độ chuyển mạch tăng lên. Công cụ lập kế hoạch vị trí CADSTAR cung cấp một bộ đầy đủ các tiện ích thiết lập vị trí và bảng (ví dụ: chồng xếp lớp, quy tắc thiết kế, v.v.) để cung cấp cho các kỹ sư thiết kế các công cụ để xác định vị trí quan trọng.